# **Final Report**

C-Biscuits, Team 4 Caleb Harper Lissa Avery Matt Salisbury Mike Turpyn

# **Table of Contents**

| FABLE OF CONTENTS                             | 2    |

|-----------------------------------------------|------|

| EXECUTIVE SUMMARY                             | 4    |

| NTRODUCTION                                   | 5    |

| SUMMARY OF DESIGN                             | 6    |

| CONCLUSION                                    | 8    |

| APPENDIX A – DESIGN DOCUMENTATION             | 9    |

| INSTRUCTIONS AND USAGE                        | 9    |

| Introduction                                  | 9    |

| R1- and R2-Type Instructions                  |      |

| Addition                                      |      |

| Subtraction                                   |      |

| Store Word                                    |      |

| Set Less Than                                 |      |

| Shift Left Logical                            |      |

| And                                           |      |

| Or                                            |      |

| Load Word                                     |      |

| B-Type Instructions                           |      |

| Branch If Not Equal                           |      |

| C-Type Instructions                           |      |

| Load Upper Immediate                          |      |

| Load Lower Immediate                          |      |

| Jump Register and Link                        |      |

| Load Address                                  |      |

| Move To Co-Processor                          |      |

| REGISTERS AND CONVENTIONS                     |      |

| INSTRUCTION FORMATS                           |      |

| R1 Type Instructions                          |      |

| R2 Type Instructions                          |      |

| B Type Instructions                           | 15   |

| C Type Instructions                           | . 16 |

| INSTRUCTION TRANSLATION TO MACHINE LANGUAGE   | . 17 |

| R1-Type Instructions                          | . 17 |

| slt                                           |      |

| sll                                           | . 17 |

| or                                            | . 17 |

| and                                           | . 17 |

| R2 Type Instructions                          | . 17 |

| add                                           | . 17 |

| sub                                           | . 18 |

| lw                                            | . 18 |

| SW                                            | . 18 |

| C Type Instructions                           | . 18 |

| lli                                           | . 18 |

| lui                                           | . 18 |

| la                                            | . 18 |

| jalr                                          | . 18 |

| mtc0                                          |      |

| mfc0                                          |      |

| B Type Instructions                           | . 19 |

| bne                                           | . 19 |

| EXAMPLE ASSEMBLY-LANGUAGE PROGRAMS            | . 20 |

| Euclid's Algorithm                            | . 20 |

| Implementation of Exam 1 Earnings Calculation |      |

| Exception-Handling Code                 | 23 |

|-----------------------------------------|----|

| Machine Code – Euclid's Algorithm       | 24 |

| Machine Code – Earnings Calculation     | 25 |

| LIST OF COMPONENTS AND THEIR INTERFACES | 27 |

| DESCRIPTIONS OF COMPONENTS              | 29 |

| RTL DESCRIPTION OF INSTRUCTIONS         | 30 |

| BLOCK DESIGN                            | 31 |

| CONTROL SIGNALS                         | 32 |

| One-bit control signals                 | 32 |

| Two-bit control signals                 | 32 |

| Three-bit control signals               | 33 |

| CONTROL UNITS                           | 34 |

| CONTROL TESTS                           | 40 |

| COMPONENT SPECIFICATION                 | 44 |

| Control unit creation                   | 44 |

| ALU design and creation                 | 44 |

| Memory creation                         | 45 |

| Instruction Register                    | 46 |

| Register File                           | 46 |

| Co-Register File                        | 46 |

| INTEGRATION PLAN                        | 48 |

| APPENDIX B – DESIGN JOURNAL             | 49 |

| APPENDIX C – TEST RESULTS               | 54 |

| ALU                                     | 54 |

| Control and user inputs                 |    |

| Memory                                  |    |

| Instruction Register                    |    |

| Register File                           |    |

| Co-Register File                        |    |

| Integrated Unit                         |    |

|                                         |    |

# **Executive Summary**

For the final project in CS232, we were to design "a miniscule instruction set." We were then asked to model our design, test it, debug it, assess its performance, and possibly implement it on a Field Programmable Gate Array (FPGA) microchip. This executive summary is intended to give the reader a brief summary of our design flow and our current status.

For the first milestone of our project, we had to design the foundation of our processor. We decided we would have 16 registers. We thought it would be convenient to have a "zero" register. Other registers included two argument registers, three temporary registers, three saved temporary registers, two kernel registers, a stack register, a return address register, a register for the assembler, a register for the results, and a display register. We also decided in milestone I to have four different instruction types: R1, R2, C, and B types.

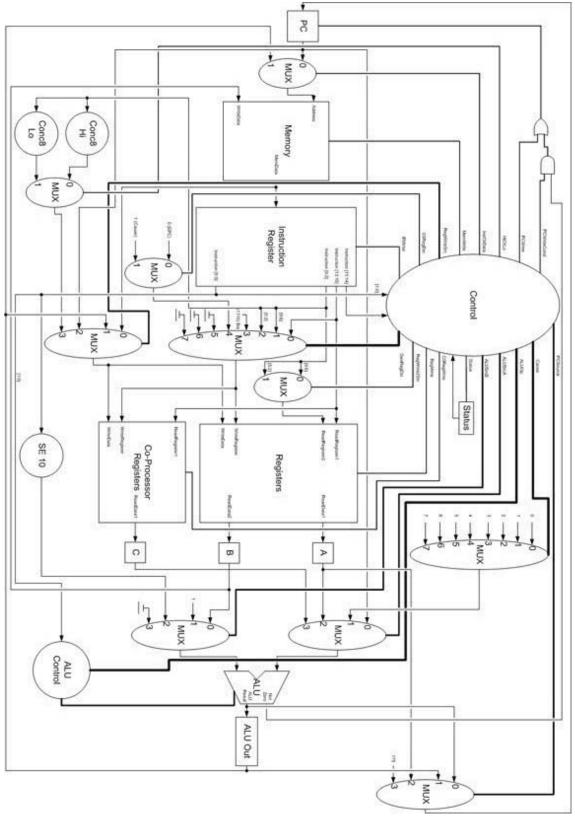

For the next milestone, we decided on certain components we would need for our processor. These parts included a memory, instruction register, register file, temporary registers, an ALU, a Sign Extend, and a concatenate part. The basic functionalities of each part can be found in our design document. Also in milestone II, we designed our first RTL (which also can be found in our design document).

For milestone III, we had to produce the first model of the datapath. We decided to keep our datapath similar to MIPS because we understood it better than other processor types, and we could use MIPS as a model for future development. Another section of milestone III was determining the function of each control signal. We ended up having 18 different control signals. Also in milestone III, we had to define a test plan for our processor. We felt that our test plan was extensive and covered every functionality required so that our processor could be successful.

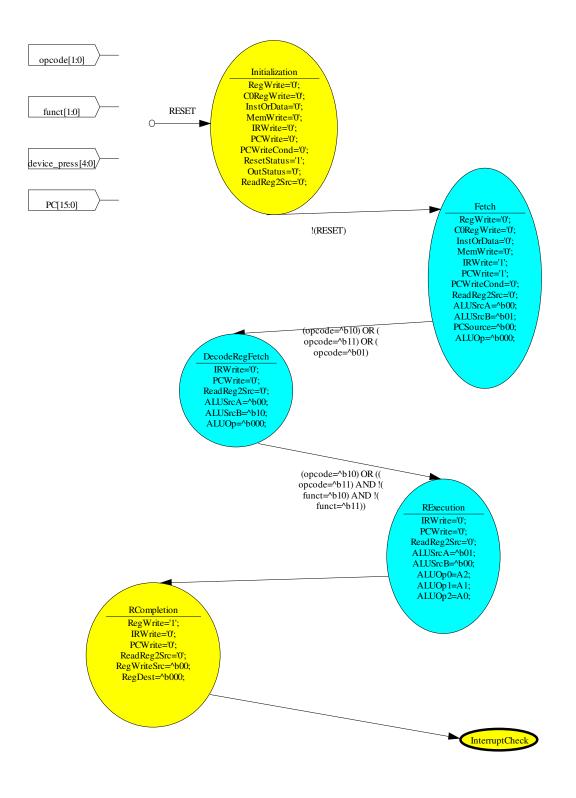

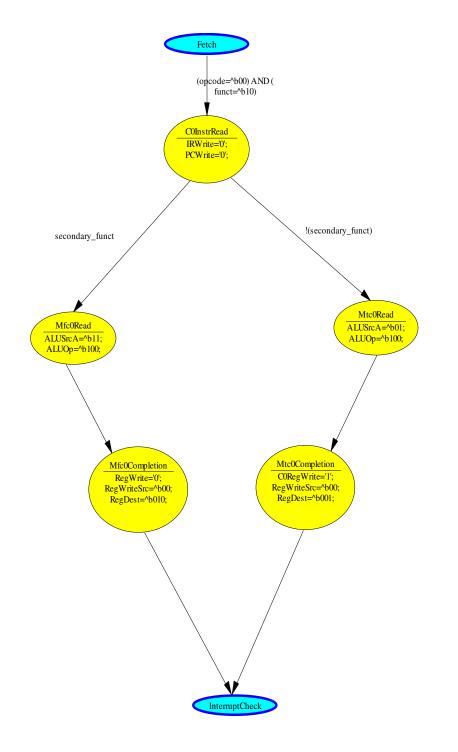

In milestone IV, we designed our control component. Our processor's control was implemented using a finite state machine. The combinational logic unit, called the ALUOp Calculator, uses the Op code and function code, both of which are inputs to the Control, to determine the appropriate ALUOp for the instruction. Also in this section we had to develop a test plan for the control part. Our test included several simulations to ensure correct transitions.

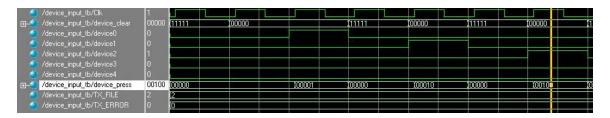

For the last milestone of the project, we needed to implement our components into Xilinx. Each one of us was assigned various parts to complete. We were supposed to design, test, and create a part of each one of our components. We felt that if each individual part was tested that it would ensure that our final product would be successful. We used ModelSim to test our individually components, partly because Caleb understood how to use it, and also because upperclassmen who completed the project in the past recommended testing everything using ModelSim.

In the end, the processor was capable of executing several instructions—including branching, storing and loading words to and from memory, and R-type instructions—but not the entire GCD program. Several issues with developed with Xilinx and the integration of the components during the last few hours of project time that hindered our success. This includes a problem when the entire processor was moved from one team member's computer to another's that caused an error ingenerating timing reports and gate counts.

# Introduction

The purpose of the project described in this document is to design a small instruction set and model it using Xilinx software. The instruction set was designed to operate on a 16-bit microprocessor, also designed in this project.

The team was given a problem—to find a number relatively prime to a given number using Euclid's algorithm—for which it designed an instruction set to solve. The instruction set needed to be sufficiently robust to be able to handle nested procedures, parameters, and general computations not necessarily needed for the execution of Euclid's algorithm.

In addition to these basic requirements, the processor outlined here supports recursive procedures through stack memory usage and interrupts from five input devices.

Beginning with some knowledge of the 32-bit MIPS instruction set and how that might be implemented, the team devised a 16-bit instruction set meeting the above requirements. The design includes the actual instructions and their translation to machine code, the register transfer language instructions to execute the programmer-level instructions, and a corresponding datapath.

Following this design, the datapath was constructed and tested in Xilinx. CoreGen use was permitted where applicable, and StateCAD/Verilog use was permitted for the control units.

Testing followed implementation. All components were tested using test benches in ModelSim, but the control finite state machine unit underwent preliminary exhaustive testing in StateCAD's StateBench.

# Summary of Design

Our initial design phase consisted of choosing what types of instructions we planned to include in our architecture. Using Euclid's algorithm as a source, we translated a version of the algorithm from Java to assembly. This process allowed us to determine what instructions were absolute necessities, and which instructions were optional. Pages 49 and beyond of the accompanying design journal (Appendix B) has detailed descriptions of each instruction type as well as each individual instruction. In order to leave as many options open in the event a future revision was required, our group created a single branch instruction. This *branch if not equal* instruction assumes the role of its counterpart; however, it requires manipulation on the part of the programmer. Additional drawbacks include the limited ability to branch at most 31 instructions in either direction. This has obvious limitations in the size and scope of any program written in our assembly language. Nevertheless, this instruction fulfills the requirements for the specified program.

Most notable deviations from the standard MIPS instruction set are the following instructions: *jump register and link, load address, move to co-processor,* and *move-from-coprocessor.* In an effort to make our instruction set as compact and efficient as possible, we combined the three MIPS jump instructions into one single instruction. This instruction jumps to the value of the given register, and automatically stores the value of the PC in the return register. While this shortens our instruction list, it makes programming slightly more difficult. The programmer must be aware that they will change the return address every time that they perform a jump.

The load address instruction is actually a pseudo-instruction that places the memory location of the given label into the given register. We initially wanted to avoid the inclusion of pseudo-instructions in our architecture to keep things as simple as possible, however we eventually decided the benefits to the programmer outweighed the slight complication of our instruction set. The final design of the load address instruction condensed a *load upper, load lower*, and *or* instruction all into one instruction.

Another design choice was the decision to treat labels as immediate values for branching purposes. While this simplified our instruction set, it limits the distance that can be branched to the length of an immediate value. However, since this value was already limited by other constraints, we did not actually need to make any additional tradeoffs to make this change. It was simply an easier method to implement labels within our architecture.

In order to more easily handle exceptions, we included room for manipulation of the exception data in our main instruction set. We needed some means of moving the data to and from the cause register, and solved this problem by creating a *move to co-processor, move-from-coprocessor*. Although the addition of these instructions limited the number of other instructions that we could include, we found enough room to include everything.

Once we had determined which instructions would be included in our architecture, we needed to finalize the format for each type of instruction. Loosely basing our design off of MIPS, we began each instruction with the operation code, and ended them with the function code. This was done to make the processor easier to wire when it came time to actually build the design.

The second major issue that we addressed in our initial design phase was the number of registers to include. We wanted to include a power of two, to limit the number of wasted bits in our design. We compiled a list of all of the registers that would be a necessity and then rounded up to the nearest power of two. A full list of the registers and their purposes can be found on pages 8 and 9 of the design journal.

There were three design changes at this point in the project that our group would consider were we able to do the project again. The first of these changes would be to increase the amount of temporary registers available. This would allow for greater versatility when programming. The drawback, however, is that there was little to no room in our current design to fit these. If they were added, then another bit would need to be included to account for the extra register, but this would greatly affect our instruction design. At

that point, it might be easier to expand the processor to 32 bits instead. Another option for our group was to intentionally increase the number of register up to 64 from 16. This idea would have the same drawbacks as the previous idea; however, we now have additional registers to work with. A possible solution would be to specify particular registers to particular instructions. Another design change we might want to make is the addition of more pseudo-instructions, such as a load immediate instruction. This would make things easier for the programmer, while not affect the performance of the processor, as the compiler would take care of the translation to machine code. Once we finalized our instruction set, register conventions, and op-code designations, we were ready to move on to the next phase of our project.

The second phase of our project consisted of an RTL description of each instruction type and a list of the processor components we wanted to include, and specifically what each one would accomplish. Page 30 (Appendix A) shows the RTL description of our group's architecture. The benefits of our datapath design are the relatively few clock cycles that our instructions require. The tradeoff here is that our datapath and control became more complicated, however from a performance standpoint; a lower CPI is preferable to a simplified datapath.

Our component list looked very similar to the list of components for the MIPS instruction set. A list of our components and their inputs and outputs as well as a brief description of each can be found on page 27. However, there were some noticeable design difference between our list and the MIPS list. The first of these is the number of control bits in Memory. MIPS uses two 1-bit control bits, MemRead and MemWrite. The inclusion of MemRead is only for the Memory data register. Our more simplified design did not require such a register, and so we had no need for its accompanying control bit. Other design choices include a separate set of co-processor registers to deal with the mfc0 and mtc0 instructions. This register block is designed to hold the EPC and Cause registers, as well as Display and other co-processes. While this will add additional components to our datapath, we felt the accessibility of these registers and resulting ease of exception handling was a good design tradeoff.

Another design decision was the inclusion of the Status register as a separate component. A control bit is sent directly to the Status register, and it is wired directly back to control. This register not only prevents one exception from interrupting another, leading to an infinite loop, but also does so as soon as it changes, disregarding any triggering from the processor clock.

To facilitate the implementation of our branch instruction, the ALU was given an output bit called NotZero. This value was a 1 if the two inputs were not equal and 0 if they were equal. We believe that this output would simplify the branch instruction without adding any drawbacks.

The next phase of our design process required our group to create both the block diagram of our datapath. When dealing with the two exception instructions, however, we chose to simplify control by adding another clock cycle to the instructions. In this case, however, since exceptions will not account for the majority of the instructions, we felt that this was an acceptable tradeoff to ensure that our group could finish and test our processor before the deadline.

While creating the datapath, we found that we needed to make some adjustments in the way that our design was implemented. Almost all of these changes were done by using multiplexers. While this added additional components and control bits to our design, it made further modifications much easier. Also, if we decided to undo one of the changes that we had made, it would be a simple process of removing the multiplexer.

If the number of registers in our project design was increased, then it would have possible to eliminate the co-processor register block from our datapath by combining it with our normal register block. While this design would have all of the drawbacks mentioned in the previous changes, it would have an additional advantage of a simpler datapath. Not only could we follow the same path for the exception instructions, but the control bits would be eliminated, making the creation of the processor much easier. Another change that our group would make if we were able to do the project again would be to write the user input to control instead of the display register.

# Conclusion

As mentioned in the Executive Summary, the processor is not working completely according to specifications, making performance information not the most accurate. Although not all data can be directly obtained, some can be calculated or derived from what we *can* get.

Our instruction set required 56 instructions to calculate the greatest common denominator using Euclid's algorithm. This yields a CPI of 4.219.

The processor's clock cycle frequency is 7.193 MHz, which leads to a cycle time of 139 ns.

For the calculation of a number relatively prime to 0x13B0, the execution of 470 instructions are required to obtain a result of 0x000B, which gives a cycle count of 1982.93 and an execution time of 275.67 ns.

Problems with Xilinx file migrations prevented the obtainment of a complete gate count of the processor.

# **Appendix A – Design Documentation**

### Instructions and usage

#### Introduction

The following document details the instructions which will be performed by our processor. Due to the limitations of a 16-bit machine, several of our instructions have been condensed to the point that an ill-prepared user might get into trouble. Please pay special attention to all notes marked with an asterisk '\*'. These provide essential warnings for our instruction set.

#### Example

| 'command' 'argument' | Ор | \$rt | 0 | Func |

|----------------------|----|------|---|------|

|                      | 2  | 4    | 8 | 2    |

This is just an example to help demonstrate the format of the instructions. The operation code ("Op code") and function bits contain the appropriate information to select the particular instruction desired. Some commands have no function code. The other bits contain either the address of a register or an immediate value, depending on the particular command. The numbers underneath the table detail the number of bits that each part of the instructions occupies.

### **R1- and R2-Type Instructions**

#### Addition

| add | \$rd, \$rs, \$rt | Op | \$rs | \$rt | \$rd | Func |

|-----|------------------|----|------|------|------|------|

|     |                  | 2  | 4    | 4    | 4    | 2    |

The *add* command sums the values of the registers in the registers \$rt and \$rs, then stores the value in the register \$rd.

### Subtraction

| sub | \$rd, \$rs, \$rt | Op | \$rs | \$rt | \$rd | Func |

|-----|------------------|----|------|------|------|------|

|     |                  | 2  | 4    | 4    | 4    | 2    |

Similar to the add command, the sub command takes the value in register \$rs, subtracts from it the value in register \$rt, and stores the value in register \$rd.

#### **Store Word**

| SW | \$rd, \$rs, \$rt | Op | \$rs | \$rt | \$rd | Func |

|----|------------------|----|------|------|------|------|

|    |                  | 2  | 4    | 4    | 4    | 2    |

The format of sw is slightly different than the standard MIPS instruction. The \$rd register contains the value which is to be stored into memory, the \$rs register contains the address of the destination in memory, and the \$rd register contains the offset of the memory address.

#### Set Less Than

| slt | \$rd, \$rs, \$rt | Op | \$rs | \$rt | \$rd | Func |

|-----|------------------|----|------|------|------|------|

|     |                  | 2  | 4    | 4    | 4    | 2    |

The slt instruction changes the value of register \$rd based on the value of \$rs relative to register \$rt. If the value in register \$rs is less than the value in register \$rt, then the value of \$rd is set to 1. Otherwise, the vale of \$rd is set to 0.

### **Shift Left Logical**

| sub | \$rd, \$rs, \$rt | Op | \$rs | \$rt | \$rd | Func |

|-----|------------------|----|------|------|------|------|

|     |                  | 2  | 4    | 4    | 4    | 2    |

In this instruction set, the shift left logical command is formatted as displayed above. The value in register \$rs is shifted to the left by the amount in the register \$rd, the resultant calculation is stored into register \$rd.

#### And

| and | \$rd, \$rs, \$rt | Op | \$rs | \$rt | \$rd | Func |

|-----|------------------|----|------|------|------|------|

|     |                  | 2  | 4    | 4    | 4    | 2    |

This instruction performs a bitwise logical nand on two registers, \$rs and \$rt and stores the resulting value into register \$rd.

#### Or

| or | \$rd, \$rs, \$rt | Op | \$rs | \$rt | \$rd | Func |

|----|------------------|----|------|------|------|------|

|    |                  | 2  | 4    | 4    | 4    | 2    |

This instruction performs a bitwise logical or on two registers, \$rs and \$rt and stores the resulting value into register \$rd.

#### Load Word

| lw | \$rd, \$rs, \$rt | Op | \$rs | \$rt | \$rd | Func |

|----|------------------|----|------|------|------|------|

|    |                  | 2  | 4    | 4    | 4    | 2    |

The format of lw is slightly different than the standard MIPS instruction. The \$rd register contains the value which is to be loaded from memory, the \$rs register contains the address of the memory destination, and the \$rd register contains the offset of the memory address.

### **B-Type Instructions**

# Branch If Not Equalbne\$rs, \$rt, labelOp\$rs\$rtOffset2446

Since all branch type commands can be calculated using either branch if not equal or branch if equal, and given the limited space for instructions, only one of the branch instructions was included in the instruction

lui

set. The command compares the values in registers \$rs and \$rt, and if the two are not equal it tries to branch to the address of label.

\* The maximum distance bne can go is  $2^5 - 1 = 31$  instructions forward or backward.

### **C-Type Instructions**

### Load Upper Immediate

| \$rt, imm | Op | \$rs | Immediate | Func |

|-----------|----|------|-----------|------|

|           | 2  | 4    | 8         | 2    |

The load upper immediate manipulates the eight most significant bits in a given register. It replaces the eight upper bits in the register \$rs with the value specified in the immediate field, and the lower eight bits are subsequently replaced with zeros.

### Load Lower Immediate

| lli | \$rt, imm | Op | \$rs | Immediate | Func |

|-----|-----------|----|------|-----------|------|

|     |           | 2  | 4    | 8         | 2    |

The load lower immediate manipulates the eight least significant bits in a given register. It replaces the lower bits in the register \$rs with the value specified in the immediate field, and the upper eight bits are subsequently replaced with zeros.

### Jump Register and Link

jalr \$rt

| Op | Immediate | \$rt | Immediate | Func |

|----|-----------|------|-----------|------|

| 2  | 4         | 4    | 4         | 2    |

The jump register and link is the only jump command in the instruction set. It jumps to the value specified in register \$rs, and it also automatically loads the return value (current value of the PC register) into the register \$ra. A standard jump can be accomplished if the address for a given label is loaded into a register and the jalr command is called referencing that particular register.

### Load Address

la \$rs, label pseudoinstruction

The load address commands places the memory location of the given label into register \$rs.

### **Move To Co-Processor**

| mtc0 | \$rs, \$co | Op | \$rs | c0 | Extra | Secondary<br>Func | Func |

|------|------------|----|------|----|-------|-------------------|------|

|      |            | 2  | 4    | 4  | 3     | 0                 | 2    |

This command moves information from a general purpose register to one of the registers in the coprocessor. This command is especially important for interrupt and exception handling. The information specified in the co-processor register \$co will be overwritten upon completion of the command.

### **Move From Co-Processor**

| mfc0 | \$rs, \$co | Op | \$rs | c0 | Extra | Secondary<br>Func | Func |

|------|------------|----|------|----|-------|-------------------|------|

|      |            | 2  | 4    | 4  | 3     | 1                 | 2    |

This command moves information from one of the co-processor register to one of the general purpose registers. The information in the general purpose register \$rs will be overwritten when the data is moved. This command is used primarily for dealing with interrupts and exceptions.

| Register name | Number | Usage                              |  |

|---------------|--------|------------------------------------|--|

| \$zero        | 0      | Constant 0                         |  |

| \$at          | 1      | Reserved for assembler             |  |

| \$v0          | 2      | Results of a function              |  |

| \$a0          | 3      | Argument 1                         |  |

| \$a1          | 4      | Argument 2                         |  |

| \$t0          | 5      | Temporary (not saved across calls) |  |

| \$t1          | 6      | Temporary (not saved across calls) |  |

| \$t2          | 7      | Temporary (not saved across calls) |  |

| \$s0          | 8      | Saved temporary                    |  |

| \$s1          | 9      | Saved temporary                    |  |

| \$s2          | 10     | Saved temporary                    |  |

| \$k0          | 11     | Kernel use only                    |  |

| \$k1          | 12     | Kernel use only                    |  |

| \$sp          | 13     | Stack pointer                      |  |

| \$ra          | 14     | Return address for function calls  |  |

| \$t3          | 15     | Temporary (not saved across calls) |  |

### **Registers and Conventions**

| Coprocessor registers | Number | Usage                                    |

|-----------------------|--------|------------------------------------------|

| \$EPC                 | 0      | Address of interrupt-causing instruction |

| \$Cause               | 1      | Interrupt type                           |

| \$display             | 2      | Output to display                        |

In addition, there is a program counter register that is not part of either register set. It holds the address of the instruction following what is currently being executed.

For optimal register usage by large-sized programs, it is best to define a set of conventions defining how and where registers can be read and written. In this processor, there are 16 general purpose registers to be managed in the defined conventions; one is wired to ground (effectively a "0" register) and cannot be written by the programmer.

| Reg # | Reg name  | Applicable Conventions                                                                                                                                                                                                                                                   |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | \$0       | Hardwired to ground, always zero                                                                                                                                                                                                                                         |

| 1     | \$at      | A temporary register used by the assembler, primarily used for storing jump<br>addresses and executing jumps. This register can be used by the coder, but should<br>be done so sparingly and with extreme caution since the value is liable to change<br>without warning |

| 2     | \$v0      | This register is used to return values from a procedure call. A value that is to be returned from a procedure should be stored here prior to returning. Extra values should be returned on the stack, following stack conventions.                                       |

| 3-4   | \$a0-\$a1 | These register are used for passing arguments into a procedure. Values that are to be passed should be loaded into these registers prior to calling the procedure. Extra values could be sent on the stack, as long as the caller follow proper stack convention         |

| 5-8   | \$t0-\$t3 | These registers are for temporary data. There is no guarantee that they will be saved across calls                                                                                                                                          |

|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9-11  | \$s0-\$s2 | These registers are for saved data. Before these registers can be used, the values must be stored by the callee to the stack; the original values should then be restored before returning to the calling function.                         |

| 12-13 | \$k0-\$k1 | These are registers used by the processor for exception calls. They should NOT be used by the coder.                                                                                                                                        |

| 14    | \$sp      | The stack pointer register points to the current position on the stack. Any modifications made to this register should ultimately be 'undone' prior to returning (i.e. if 4 is subtracted from \$sp, then 4 must be added before returning) |

| 15    | \$ra      | This register will contain the return address anytime a jalr command is used. It should NOT be used by the coder except to obtain the return address for a later purpose                                                                    |

### Instruction Formats

### **R1 Type Instructions**

| opcode | rs    | rt    | rd    | func code |

|--------|-------|-------|-------|-----------|

| 2-bit  | 4-bit | 4-bit | 4-bit | 2-bit     |

opcode = Basic operation of the instruction

func code = This field selects the specific variant of the operation in the opcode field.

rs = The first register source operand

rt = The second register source operand

rd = the register destination operand (gets the result of the operation).

### **R2 Type Instructions**

| opcode | rs    | rt    | rd    | func code |

|--------|-------|-------|-------|-----------|

| 2-bit  | 4-bit | 4-bit | 4-bit | 2-bit     |

opcode = Basic operation of the instruction

func code = This field selects the specific variant of the operation in the opcode field.

rs = The first register source operand

rt = The second register source operand

rd = the register destination operand (gets the result of the operation).

### **B** Type Instructions

| opcode | rs    | rt    | offset |

|--------|-------|-------|--------|

| 2-bit  | 4-bit | 4-bit | 4-bit  |

opcode = Basic operation of the instruction

rs = The first register being compared

rt = The second register being compared

offset = a register when data is transferring

### **C** Type Instructions

| opcode | rt    | undesignated | func code |

|--------|-------|--------------|-----------|

| 2-bit  | 4-bit | 8-bit        | 2-bit     |

opcode = Basic operation of the instruction

func code = This field selects the specific variant of the operation in the opcode field.

rt = The register containing an address

undesignated = bits not currently being used

# Instruction translation to machine language

## **R1-Type Instructions**

Opcode - 10

### slt

| opcode | rs | rt | rd | func code |

|--------|----|----|----|-----------|

| 10     |    |    |    | 00        |

### sll

| opcode | rs | rt | rd | func code |

|--------|----|----|----|-----------|

| 10     |    |    |    | 01        |

#### or

| opcode | rs | rt | rd | func code |

|--------|----|----|----|-----------|

| 10     |    |    |    | 10        |

### and

| opcode | rs | rt | rd | func code |

|--------|----|----|----|-----------|

| 10     |    |    |    | 11        |

### **R2 Type Instructions**

Opcode - 11

### add

| opcode | rs | rt | rd | func code |

|--------|----|----|----|-----------|

| 11     |    |    |    | 00        |

11

....

### sub

| opcode | rs | rt | rd | func code |

|--------|----|----|----|-----------|

| 11     |    |    |    | 01        |

| lw     |    |    |    |           |

| opcode | rs | rt | rd | func code |

| 11     |    |    |    | 10        |

| SW     |    |    |    |           |

| opcode | rs | rt | rd | func code |

....

| С | Type | Instructions |   |

|---|------|--------------|---|

| U | IYPE | manuchona    | ) |

Opcode - 00

11

### lli

| opcode | rs | imm | func code |

|--------|----|-----|-----------|

| 00     |    |     | 00        |

....

# lui

| opcode | rs | imm | func code |

|--------|----|-----|-----------|

| 00     |    |     | 01        |

### la

pseudoinstruction

# jalr

| opcode | imm | rt | imm | func code |

|--------|-----|----|-----|-----------|

| 00     |     |    |     | 11        |

### mtc0

| opcode | rs | c0 | extra | secondary | func code |

|--------|----|----|-------|-----------|-----------|

| 00     |    |    | 0     | 0         | 10        |

### mfc0

| opcode | rs | c0 | extra | secondary<br>func | func code |

|--------|----|----|-------|-------------------|-----------|

| 00     |    |    | 0     | 1                 | 10        |

# **B** Type Instructions

Opcode - 01

### bne

| opcode | rs | rt | offset |

|--------|----|----|--------|

| 01     |    |    |        |

### Example assembly-language programs

#### **Euclid's Algorithm**

main: lli \$s0, 2 1li \$s0, 2 # set "m" to 2 initially mfc0 \$t0, \$2 # grab the "n" from the display register add \$a0, \$t0, \$0 # set our first parameter to "n" add \$a1, \$s0, \$0 # set second parameter to "m" la \$s1, loop # create our loop label for usage as a jump # site la \$s2, GCD # likewise for the GCD function loop: jalr \$s2 # call GCD lli \$t1, 1 # the constant 1; the limited registers means # this must be set every time around add \$s0, \$s0, \$t1 # increment "m" mfc0 \$t0, \$2 # grab the "n" from the display register # the scarce register situation leads to this # repetition add \$a0, \$t0, \$0 # set our first parameter to "n" add \$a1, \$s0, \$0 # set second parameter to "m" bne \$v0, \$t1, \$s1 # loop; if the return variable wasn't a one (1) # jump back and resume looping la \$t1, exit jalr \$t1 GCD: 11i \$t0, -1 # there are three saved variables to save off # to the stack lli \$t1, 1 # a good, useful constant to have add \$sp, \$sp, \$t0 # increase stack space sw \$s0, \$sp, \$0 # save the first one add \$sp, \$sp, \$t0 sw \$s1, \$sp, \$0 # and the second one... add \$sp, \$sp, \$t0 sw \$s2, \$sp, \$0 # and the final one... add \$s0, \$a0, \$0 # store parameter "n" for our usage; # also known as "a" add \$s1, \$a1, \$0 # store parameter "m" for our usage as well; # also known as "b" la \$s2, GCD\_loop add \$sp, \$sp, \$t0 sw \$ra, \$sp, \$0 # store the return address, since we are doing # a bit of internal jumping

```

GCD_loop: la $t2, return

slt $t0, $0, $s1 # if b !> 0, get out of dodge

bne $t0, $t1, $t2 # Note this is compared to a *1*, not a zero

la $t2, switcher

slt $t0, $s0, $s1 # if b > a, swap 'em.

bne $t0, $t1, $t2 # Again, this compares the slt with 1

sub $s0, $s0, $s1 # otherwise, subtract b from a and store in a

switcher: add $t2, $s0, $0 # swapperoo

add $s0, $s1, $0

add $s1, $t2, $0

jalr $s2

# back to the loop

return: add $v0, $s0, $0  # set the return variable to "a"

lli $t0, 1  # about to unload the stack

lw $ra, $sp, $0

add $sp, $sp, $t0

lw $s2, $sp, $0

add $sp, $sp, $t0

lw $s1, $sp, $0

add $sp, $sp, $t0

lw $s0, $sp, $0

add $sp, $sp, $t0

jalr $ra

```

```

exit: # done

```

#### Implementation of Exam 1 Earnings Calculation

# C-biscuit implementation of Exam 1 assembly code

```

.data

```

| numHours:<br>rate:<br>earnings: | .word 30                                                                                                                                 |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| .text                           |                                                                                                                                          |

| main:                           | <pre>lui \$at, 0 lli \$t0, numHours or \$t0, \$t0, \$at lli \$t1, rate or \$t1, \$t1, \$at add \$a0, \$t0, \$0 add \$a1, \$t1, \$0</pre> |

|                                 | la \$s0, CalcEarnings<br>jalr \$s0                                                                                                       |

|                                 | add \$t0, \$v0, \$0                                                                                                                      |

la \$s1, earnings sw \$t0, \$s1, \$0 lli \$v0, 10 syscall CalcEarnings: add \$t0, \$a0, \$0 add \$t1, \$a1, \$0 # keep same \$a0, \$a1 lui \$at, 0 lli \$t2, −2 # preparation for stack usage for return addy or \$t2, \$t2, \$at add \$sp, \$sp, \$t2 sw \$ra, \$sp, \$0 add \$sp, \$sp, \$t2 sw \$s0, \$sp, \$0 la \$t2, CalcGross jalr \$t2 add \$s0, \$v0, \$0 # snag the gross income add \$a0, \$s0, \$0 # back out for consumption #la \$t2, CalcTax #jalr \$t2 #add \$t0, \$v0, \$0 # grab calculated tax lli \$t0, \$0 sub \$t2, \$s0, \$t0 # net = gross - tax add \$v0, \$t1, \$0 11i \$t2, 2 or \$t2, \$t2, \$0 lw \$ra, \$sp, \$0 add \$sp, \$sp, \$0 lw \$s0, \$sp, \$0 add \$sp, \$sp, \$t2 jalr \$ra CalcGross: lli \$t2, -2 # preparation for stack usage for callersaved registers or \$t2, \$t2, \$0 add \$sp, \$sp, \$t2 sw \$ra, \$sp, \$0 add \$sp, \$sp, \$t2 sw \$s2, \$sp, \$0 add \$sp, \$sp, \$t2 sw \$s1, \$sp, \$0 add \$sp, \$sp, \$t2 sw \$s0, \$sp, \$0 lli \$t0, 0

or \$t0, \$t0, \$0 lli \$s0, 0 # a temp gross or \$s0, \$s0, \$0 la \$s1, cg\_loop cq\_loop: lli \$t1, 1 or \$t1, \$t1, \$0 add \$s0, \$s0, \$a1 # add the rate to the gross again add \$t0, \$t0, \$t1 slt \$t2, \$t0, \$a0 # while our counter is less than the # number of hours, add the rate to # itself. Horrible multiplication bne \$t2, \$t1, \$s1 # hop back to re-loop # done with looping add \$v0, \$s0, \$0 lli \$t2, 2 # preparation for stack usage for caller # saved registers or \$t2, \$t2, \$0 sw \$s0, \$sp, \$0 add \$sp, \$sp, \$t2 sw \$s1, \$sp, \$0 add \$sp, \$sp, \$t2 sw \$s2, \$sp, \$0 add \$sp, \$sp, \$t2 sw \$ra, \$sp, \$0 add \$sp, \$sp, \$t2 jalr \$ra

#### **Exception-Handling Code**

|             | lli \$at, -1<br>add \$sp, \$at, \$0<br>sw \$t3, \$sp, \$0                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | <pre>mfc0 \$t3, \$Cause bne \$t3, \$0, BeginEuclid #If we have the second interrupt,</pre>                                                                                                                   |

|             | <pre>we're dealing with the loading of the number<br/>lli \$k0, 176<br/>lui \$k1, 19<br/>or \$k0, \$k0, \$k1<br/>mtc0 \$Display, \$k1<br/>bne \$k0, \$0, Wait</pre>                                          |

| BeginEuclid | : lli \$at, 1<br>add \$sp, \$at, \$0<br>lw \$t3, \$sp, \$0                                                                                                                                                   |

|             | <pre>mfc0 \$k0, \$EPC jalr \$k0 #Unfortunately, this kills whatever was in \$ra     # previously; a flaw, although in our case, there     # shouldn't be anything in \$ra when this is     # executed.</pre> |

Wait: #We need to exit and wait for the next interrupt. We don't # have an instruction for this--a flaw, alas.

### Machine Code – Euclid's Algorithm

| 0x2008<br>0x1486<br>0x291c<br>0x2a40<br>0x1428<br>0x1801<br>0xa95a<br>0x1454<br>0x1801<br>0xad5a                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x02c3<br>0x1801<br>0xad5a<br>0x2c03<br>0x1801<br>0xe658<br>0x1486<br>0xcd40<br>0xd240<br>0x49b9<br>0x14e0<br>0x1801<br>0x995a<br>0x0183          |

| 0x17fc<br>0x1804<br>0xfb94<br>0xe783<br>0xfb94<br>0xeb83<br>0xfb94<br>0xef83<br>0xe4c0<br>0xe900<br>0x1490<br>0x1801<br>0xad5a<br>0xfb94<br>0xf83 |

| 0x9428<br>0x5588<br>0x9668<br>0x5581<br>0xe669                                                                                                    |

| 0xde40<br>0xe680<br>0xe9c0                                                                                                                        |

0x02c3

0xce40 0x1404 0xff82 0xfb94 0xef82 0xfb94 0xeb82 0xfb94 0xe782 0xfb94 0xe782 0xfb94

### Machine Code – Earnings Calculation

0x0500 0x0608 0xc503 0xc604 0x282c 0x3806 0xc205 0x0980 0xf905 0x020a 0x4001 0xc305 0xc406 0x07fe 0xcd7d 0xfd0e 0xcd7d 0xfd08 0x277c 0x270c 0xc208 0xc803 0x0500 0xd857 0xc602 0x0702 0xed0e 0xcd0d 0xed08 0xcd7d 0x3e01 0x07fe 0xcd7d 0xfd0e 0xcd7d 0xfd0a 0xcd7d 0xfd09 0xcd7d

0xfd08 0x0500 0x0800 0x29ac 0x0601 0xc848 0xc565 0x8537 0x5dbc 0xc802 0x0702 0xfd08 0xcd7d 0xfd0a 0xcd7d 0xfd0e 0xcd7d 0x3e00

### List of components and their interfaces

#### **Program Counter (PC)**

Input: 16-bit address selected from multiplexor. Output: 16-bit address Controls: PCWrite: 1-bit bus

#### Memory

Inputs: 16-bit address from ALUOut or PC; 16-bits of data from register B Output: 16-bit contents of a memory location Controls: MemWrite: 1-bit

#### **Instruction Register (IR)**

Input: 16-bit instruction from memory Output: 16-bit instruction Control: InstructionWrite: 1-bit

#### **Register File (Reg)**

Inputs: two 4-bit Read Registers; one 4-bit Write Register; one 16-bit Write Data Outputs: 16-bit Read Data 1 and 2. Control: 1-bit RegWrite

#### **Co-processor Register File (C0Reg)**

Inputs: one 4-bit Read Register; one 4-bit Write Register; one 16-bit Write Data Outputs: 16-bit Read Data 1. Control: 1-bit RegWrite

#### Register A (A)

Inputs: 16-bits of data from the Register File (Read Data 1) Output: unaltered 16-bits of data Control: none

#### **Register B (B)**

Inputs: 16-bits of data from the Register File (Read Data 2) Output: unaltered 16-bits of data Control: none

#### Register C (C)

Inputs: 16-bits of data from the Co-processor Register File (Read Data) Output: unaltered 16-bits of data Control: none

#### Status Register (Status)

Inputs: none Output: none Control: 1-bit Status

#### Arithmetic Logic Unit (ALU) Inputs: two 16-bit operands Output: 1-bit NotZero: 16-bit ALUE

Output: 1-bit NotZero; 16-bit ALUResult Control: 4-bit operation

#### ALUOut Register (ALUOut)

Input: 16-bit ALUResult Output: 16-bit ALUResult, unaltered Control: none

#### Sign Extend by 10 bits

Inputs: 6-bit branch offset Ouput: 16-bit sign-extended word address Control: none

#### Concatenate right by 8 (Conc8 Hi)

Inputs: 8-bit immediate Output: 16-bit number with immediate in upper bits Control: none

#### Concatenate left by 8 (Conc8 Low)

Input: 8-bit immediate Output: 16-bit number with immediate in lower bits Control: none

### Descriptions of components

The program counter (PC) contains the 16-bit address of the instruction to be executed after the current instruction. Its value comes from the increment of the address (which is done via the addition of two to the current PC value), a jump address, or a branch address. Its only output is its own 16-bit value. It accepts one bit from the control specifying whether to its contents should be rewritten with waiting values.

The memory holds user-accessible data, accessible by 16-bit address. Given a 16-bit address from ALUOut or the PC, a 16-bit instruction or piece of datum, whichever lies at the given address, can be output. In this case, the one-bit MemRead control input must be enabled. For data to be written to memory, the one-bit MemWrite control input must be enabled. Likewise, the memory component will accept 16-bits of data from register B, to be placed in the address given by ALUOut.

The instruction register (IR) is a temporary register used for holding an entire instruction before it is decoded. It takes its 16-bit value from memory when the 1-bit InstructionWrite control is enabled, and outputs that same value for instruction decoding.

The register file (Reg) holds the contents of the processor's 16 general-use registers, accessible by four-bit number. Given two four-bit register numbers, the 16-bit contents of those two registers are output to Read Data 1 and Read Data 2. When the RegWrite control bit is asserted, the contents of the 16-bit Write Data input are written to the register indicated by the four-bit Write Register input.

Registers A and B are temporary registers used for holding the contents of a register (each) before they are processed further. They always write their contents at the appropriate time, so there are no control signals. The contents are obtained from the Register File's Read Data 1 and Read Data 2 for Registers A and B, respectively.

The co-processor's register file (COReg) holds three 16-bit registers, accessible by four-bit number. Given a four-bit register number, the 16-bit contents of that register are output to Read Data. When the CORegWrite control signal is assert, the data at the 16-bit Write Date input are written to the register indicated by the four-bit Write Register input.

Register C is a temporary register used for holding the value from the co-processor's register file's Read Data output.

The Status register stops the processor from accepting more than one exception at a time.

The Arithmetic Logic Unit (ALU) performs the primary mathematical operations of the processor. Given two operands, it will perform an operation on them (as determined by the ALUOp control signal) and output the result. In addition, the ALU subtracts the two operands and asserts a NotZero output if the two numbers are unequal.

The ALUOut register (ALUOut) is another temporary register that is perpetually in write-mode. It obtains and holds the results of an ALU operation for a clock cycle.

There are also several concatenate left and right components and a sign extension component. These are simply hard-wired components used to properly place or multiply numbers and have no control signals.

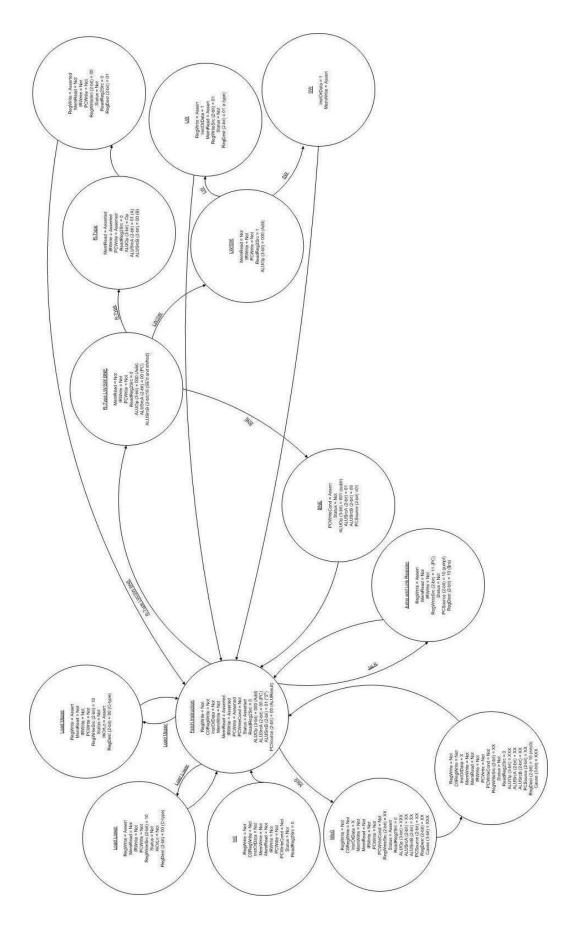

## **RTL Description of Instructions**

We broke our instructions down into 5 different sets of RTL blocks depending on the instruction. All of our R-type instructions will be executed with practically the same RTL, the LW (Load Word) and SW (Store Word) will require slight modifications.

In the C-type, the LLI (Load Lower Immediate) and LUI (Load Upper Immediate) will both have similar RTL blocks, but the JALR (Jump And Link Register) will be different, and will have its own set. Finally, the BNE (Branch if Not Equal) instruction will have an RTL chunk all to itself.

We differ slightly from MIPS in that only the first step is common amongst all of our different instructions. Differences occur in the second step, which allows us to do our jump command in just two steps instead of three. It does, however, complicate the control logic, but, hopefully, our small number of instructions will help keep it from being overwhelming.

| Step Description  | Standard     | Load Word/            | Branch if Not    | Load Lower Immediate/    | Jump And      |

|-------------------|--------------|-----------------------|------------------|--------------------------|---------------|

|                   | R-type       | Store Word            | Equal            | Load Upper               | Link Register |

|                   |              |                       | -                | Immediate                |               |

| Get Instruction & |              | Inst                  | ruction Register | <= Memory[PC]            | •             |

| increment PC      |              |                       | PČ<= P           |                          |               |

|                   |              |                       |                  |                          |               |

|                   | 1            | A <= Reg([IR[13:10]]) | ])               | Upper: reg([IR[13:10])<= | \$ra<= PC     |

|                   |              | B<= Reg(IR[9:6])      |                  | IR[9:2] conc8*           |               |

|                   | ALU          | Out<=PC+(SE[5:0]      | <<1)             |                          | PC<=          |

|                   |              |                       |                  | Lower: reg([IR[13:10])<= | reg(IR[13:10] |

|                   |              |                       | -                | conc8(IR[9:2])           | )             |

|                   | ALUOut <=    | ALUOut <= A +         | If $(A != B)$    |                          |               |

|                   | A op B       | В                     | PC<=             |                          |               |

|                   |              |                       | ALUOut           |                          |               |

|                   |              | B<=                   |                  |                          |               |

|                   |              | reg[IR(5:2)]          |                  |                          |               |

|                   | Reg([IR(5:2) | Load:                 |                  |                          |               |

|                   | ]<=ALUOut    | reg([IR(5:2)] <=      |                  |                          |               |

|                   |              | Mem(ALUOut)           |                  |                          |               |

|                   |              |                       |                  |                          |               |

|                   |              | Store:                |                  |                          |               |

|                   |              |                       |                  |                          |               |

|                   |              | Mem(ALUOut            |                  |                          |               |

|                   |              | <= B                  |                  |                          |               |

| Step Description                        | mtco                        | mfco                     |  |  |  |

|-----------------------------------------|-----------------------------|--------------------------|--|--|--|

| Get Instruction &                       | Instruction Register        | <= Memory[PC]            |  |  |  |

| increment PC                            | PC<= PC+2                   |                          |  |  |  |

|                                         | A<= Reg(IR[13:10])          | C<= CoProReg(IR[9:6])    |  |  |  |

| Additional step<br>(simplifies control) | ALUout<=A                   | ALUout<=C                |  |  |  |

|                                         | CoProReg(IR[9:6]) <= ALUout | Reg(IR[13:10]) <= ALUout |  |  |  |

\*Concatenate 8-bits (0000000)

# Block Design

### **Control Signals**

This processor implementation has a multitude of one-bit control signals, along with several two-bit control signals, and one three-bit signal.

### **One-bit control signals**

The *RegWrite* control signal is a single-bit control signal that, when asserted, writes the values of the Write Data input to the general-purpose register selected by the Write Register number. When this is deasserted, it has no effect.

The *CORegWrite* control signal is a single-bit control signal that, when asserted, writes the values of the Write Data input to the co-processor register selected by the Write Register number. When this is deasserted, it has no effect.

The *InstOrData* control signal is a one-bit signal that, when asserted, uses the contents of ALUOut to specify the address of the memory unit to be accessed. When it is deasserted, the value of the PC is used.

When asserted, the *MemWrite* one-bit control signal permits the contents of the memory unit at the location given by the address input to be overwritten by the data at the Write Data input. When not asserted, this control signal has no effect.

*IRWrite* is another one-bit control signal. When asserted, the output from the memory unit is placed in the Instruction Register. When it is not asserted, there is no effect.

Similar to the *IRWrite* control signal, the *PCWrite* control signal permits the PC to be written when asserted. When deasserted, there is no effect.

When asserted, the *PCWriteCond* permits the writing of the PC if the Not Zero output from the ALU is also active.

*HiOrLo* determines whether a load upper immediate or load lower immediate instruction will take place. When it has a value of one, a concatenation of eight bits to the lower end has taken place, indicating a load upper immediate is taking place. Otherwise, a load lower is taking place.

The *ReadReg2Src* control signal selects which bits of the instruction will dictate the register chosen for reading. When zero, the instruction bits 9 thru 6 are used. Otherwise, the bits 5 thru 2 are used, which is typical of a load word or store word command.

The *CORegDest* control signal selects either the EPC (0) or the Cause (1) as the register to be written to by the Control unit.

*Status* changes the status register to indicate whether or not the program can currently process an interrupt. When asserted, the processor can*not* process an interrupt due to either being in the middle of an instruction or due to the fact that it is already handling an interrupt. When not asserted, any interrupt-handling code will be executed if necessary.

### Two-bit control signals

The *ALUSrcA* determines the source for the first operand to the ALU. When the control signal is 00, the contents of the PC are selected. When the value is 01, the data from the A register is selected. When the control signal is 10, the value selected as the cause of an exception is chosen as the first input for the ALU. Finally, when the control signal is 11, register C, the co-processor register output, is selected.

Like *ALUSrcA*, *ALUSrcB* determines the source for the second operand to the ALU. When the control signal is 00, the B register is selected. When the control signal is 01, then one (1) is selected. When the control signal is 10, then the second input to the ALU is the sign-extended word-aligned branch offset from the Instruction Register. When the control signal is 11, the value passed along is zero.

The *PCSource* determines the source for the next update of the PC. If the signal is set to 00, the ALUResult becomes the next PC value. When the control signal is 01, ALUOut (the branch target address) is the new value of the PC. A control signal of 10 sets the PC to the jump destination address. The value of the PC is set to the exception-handling address of 0x6666 when the *PCSource* control signal is set to 11.

The RegWriteSrc selects what data to write to the general-purpose registers or co-processor register, whether it be from memory (00), ALUOut (01), the PC (10), or a concatenated immediate (11).

### Three-bit control signals

The *ALUOp* determines the operation to be performed by the ALU. When the control signal is 000, the ALU performs addition on its two operands. When the control signal is 001, a set-less-than operation is performed--subtraction is performed and the NotZero output is set appropriately. When the control signal is 010, the ALU performs a bitwise and on the operands. A control signal value of 011 performs a bitwise or. If the control signal is 100, the first operand is passed through without modification. A control signal of 101 indicates a shift left logical will be performed.

The *RegDest* control signal determines the correct number of the register to be written to by the instruction, depending on the type and nature of the instruction. When the control signal is set to 000, an R1 or R2 type instruction is being executed, and the destination register is set to \$rd. When *RegDest* is set to 001, a move-to-co-processor instruction is being executed, and the write destination is \$rs in the co-processor register. When the control signal is set to 010, a C type instruction is being executed, and the destination register is set to \$rs. A control signal value of 011 indicates a jump instruction is being executed, and the destination register is correspondingly set to \$ra. A control signal of 100 allows the co-processor register selected by the *CORegDest* control signal to be used.

The *Cause* control signal selects one of up to five exceptions. There are external exceptions from up to five devices (numbered 000 thru 100).

### **Control Units**

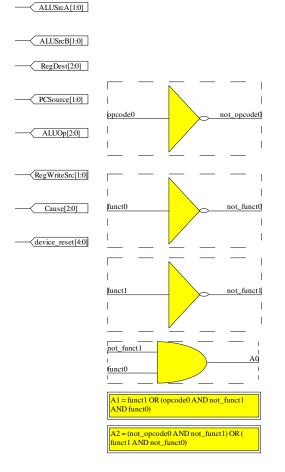

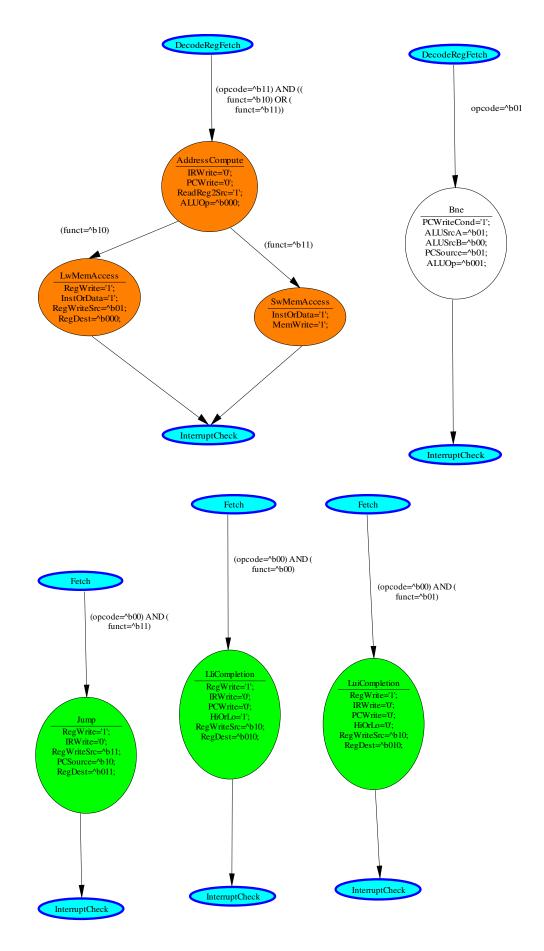

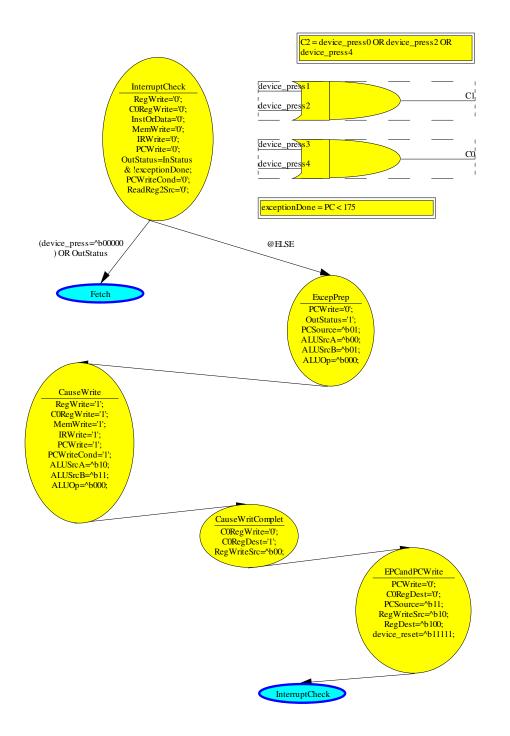

The processor's Control is implemented using a finite state machine and a portion of combinational logic.

The combinational logic unit, called the ALUOp Calculator here, uses the Op code and function code, both of which are inputs to the Control, to determine the appropriate ALUOp for the instruction.

Below is a truth table that completes this mandate. It should be noted that when the Op code is 11 and the function code is either 10 or 11, a load word or store word instruction is being processed and the state of the ALU does not matter for this branch of the state sequence.

| Opcode[0] | Opcode[1] | Funct[0] | Funct[1] | ALUOp[0] | ALUOp[1] | ALUOp[2] |

|-----------|-----------|----------|----------|----------|----------|----------|

| 1         | 0         | 0        | 0        | 0        | 0        | 1        |

| 1         | 0         | 0        | 1        | 1        | 0        | 1        |

| 1         | 0         | 1        | 0        | 0        | 1        | 1        |

| 1         | 0         | 1        | 1        | 0        | 1        | 0        |

| 1         | 1         | 0        | 0        | 0        | 0        | 0        |

| 1         | 1         | 0        | 1        | 1        | 1        | 0        |

| 1         | 1         | 1        | 0        | Х        | Х        | Х        |

| 1         | 1         | 1        | 1        | Х        | X        | Х        |

This resolves into the following equations:

ALUOp[0] = (Funct[0])' \* Funct[1] ALUOp[1] = Opcode[1] \* (Funct[0])' + Funct[0] ALUOp[2] = (Opcode[1])' \* (Funct[0])' + Funct[0] \* (Funct[1])'

Another block of combinational logic handles the interrupts. There are five devices that give interrupts in our design, although only two are implemented in software. The five different button presses are registered with individual J/K flip-flops that have enables and reset options. They are wired such that once one button press has been acknowledged, all the flip-flops are disabled until they are cleared by the Control. This ensures that only one exception occurs at a time, although it does mean that only the first button pressed during the execution of an instruction is noted.

The five devices, however, must translate into a three-bit Cause that is passed along the datapath for exception-handling. Below is the truth table for this conversion.

| Device0 | Device1 | Device2 | Device3 | Device4 | Cause[0] | Cause[1] | Cause[2] |

|---------|---------|---------|---------|---------|----------|----------|----------|

| 1       | 0       | 0       | 0       | 0       | 0        | 0        | 1        |

| 0       | 1       | 0       | 0       | 0       | 0        | 1        | 0        |

| 0       | 0       | 1       | 0       | 0       | 0        | 1        | 1        |

| 0       | 0       | 0       | 1       | 0       | 1        | 0        | 0        |

| 0       | 0       | 0       | 0       | 1       | 1        | 0        | 1        |

The primary control unit is the finite state machine described in the state transition diagram in **Appendix D**.

The system should initialize (or reset) into the state given by the control signals in the diagram below. There are several signals whose initialization values are not set, as there is nothing appropriate to set them to. For example, there is no immediately correct setting for the HiOrLo control signal, which is set to zero when the upper eight bits of an input are set to zero, indicating a load lower immediate is being performed. These "don't care" control signals are not included in this initialization state or any subsequent states. The diagram will show only those control signals that change from the previous state.

In addition, it should be noted that "assert" indicates that the control signal is active low.

## **Control Tests**

In order to ensure correct functionality of the control, several simulations need to be run to ensure correct transitions. For example, the Op code and function code for an addition statement can be input using Xilinx's State Bench application; the transitions of the state should follow the diagram above.

Omitted is the initialization state, which the processor enters upon loading.

The progression of states for a particular Op code/function code combination can be seen in the table below.

| Instruction | Op<br>code | Funct code<br>(secondary) | State progression |                                        |                |                |                |  |  |  |  |

|-------------|------------|---------------------------|-------------------|----------------------------------------|----------------|----------------|----------------|--|--|--|--|

| lli         | 00         | 00                        | Fetch             | LliCompletion                          | InterruptCheck |                |                |  |  |  |  |

| lui         | 00         | 01                        | Fetch             | LuiCompletion                          | InterruptCheck |                |                |  |  |  |  |

| jalr        | 00         | 11                        | Fetch             | Jump                                   | InterruptCheck |                |                |  |  |  |  |

| mtc0        | 00         | 10 (0)                    | Fetch             | C0InstRead                             | Mtc0Read       | Mtc0Completion | InterruptCheck |  |  |  |  |

| mfc0        | 00         | 10(1)                     | Fetch             | C0InstRead                             | Mfc0Read       | Mfc0Completion | InterruptCheck |  |  |  |  |

| bne         | 01         |                           | Fetch             | DecodeRegFetch                         | Bne            | InterruptCheck |                |  |  |  |  |

| slt         | 10         | 00                        | Fetch             | DecodeRegFetch                         | RExecution     | RCompletion    | InterruptCheck |  |  |  |  |

| sll         | 10         | 01                        | Fetch             | DecodeRegFetch                         | RExecution     | RCompletion    | InterruptCheck |  |  |  |  |

| or          | 10         | 10                        | Fetch             | DecodeRegFetch                         | RExecution     | RCompletion    | InterruptCheck |  |  |  |  |

| and         | 10         | 11                        | Fetch             | DecodeRegFetch                         | RExecution     | RCompletion    | InterruptCheck |  |  |  |  |

| add         | 11         | 00                        | Fetch             | DecodeRegFetch                         | RExecution     | RCompletion    | InterruptCheck |  |  |  |  |

| sub         | 11         | 01                        | Fetch             | DecodeRegFetch                         | RExecution     | RCompletion    | InterruptCheck |  |  |  |  |

| lw          | 11         | 10                        | Fetch             | DecodeRegFetch                         | Address        | LwMemAccess    | InterruptCheck |  |  |  |  |

|             |            |                           |                   |                                        | Compute        |                |                |  |  |  |  |

| SW          | 11         | 11                        | Fetch             | tch DecodeRegFetch Address SwMemAccess |                | InterruptCheck |                |  |  |  |  |

|             |            |                           |                   |                                        | Compute        |                |                |  |  |  |  |

Following the test of the state transitions, it is necessary to ensure that all outputs are valid. For example, using the truth table in the previous section for the combinational logic, it should be possible to execute each R-type instruction and verify that the correct ALUOp code is output.

For each state, the below tables can be used to verify the output of the Control. The initialization step includes the "don't care" signals for the sake of creating a single comprehensive list of control signals. Subsequent states only show those signals that change value. Because the processor's components are active low, not asserted means a value of one. Selectors for multiplexers have actual values.

| Control Signal      | Value        |

|---------------------|--------------|

| RegWrite            | Not asserted |

| CORegWrite          | Not asserted |

| InstOrData          | 0            |

| MemWrite            | Not asserted |

| IRWrite             | Not asserted |

| PCWrite             | Not asserted |

| PCWriteCond         | Not asserted |

| RegWriteSrc (2-bit) | Don't care   |

| Status              | Not asserted |

| HiOrLo              | Don't care   |

| ReadReg2Src         | 0            |

| ALUOp (3-bit)       | Don't care   |

| ALUSrcA (2-bit)     | Don't care   |

| ALUSrcB (2-bit)     | Don't care   |

| PCSource (2-bit)    | Don't care   |

Init

|                   | RegDest (3-bit)                                                                                                                                                                                                                                   | Don't care                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                   | Cause (3-bit)                                                                                                                                                                                                                                     | Don't care                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                   | Cause (3-bit)                                                                                                                                                                                                                                     | Doirt care                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Fetch Instruction | Control Signal                                                                                                                                                                                                                                    | Value                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| reten mstruction  | IRWrite                                                                                                                                                                                                                                           | Asserted                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                   | PCWrite                                                                                                                                                                                                                                           | Asserted                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                   | Status                                                                                                                                                                                                                                            | Asserted                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                   | ReadReg2Src                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                   | ALUOp (3-bit)                                                                                                                                                                                                                                     | 000 (Add)                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                   | ALUSrcA (2-bit)                                                                                                                                                                                                                                   | 00 (PC)                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |